Напівпровідникова пластина

Напівпровідникова пластина, підкладка (англ. wafer) — тонка монокристалічна напівпровідникова пластина, що призначена для створення плівок, гетероструктур, та вирощування монокристалічних шарів за допомогою епітаксії, кристалізації та ін. Використовується як основа для мікроелектронних пристроїв, інтегральних мікросхем. Підкладка проходить багатоетапний процес виготовлення, що включає легування, травлення, осадження різних матеріалів та фотолітографію[1].

В процесі вирощування кристалів вагому роль відіграє відповідність кристалічної решітки кремнієвої пластини кристалу, що наростає. Зокрема вагомим є структурно-геометрична відповідність, а також відсутність дефектів у підкладці. У випадку сильної невідповідності кристалічних решіток підкладки і кристалу, використовують буферний шар для попередження виникнення численних дислокацій.

Історія[ред. | ред. код]

У 50-х роках Мохамед Аталла досліджував поверхневі властивості кремнієвих напівпровідників у Bell Labs, де він застосував новий метод виготовлення напівпровідникових пристроїв, покривши кремнієву пластину ізоляційним шаром оксиду кремнію, щоб електрони могли надійно проникати до напівпровідного кремнію внизу, долаючи поверхневі стани, які заважали їм досягати напівпровідного шару. Це явище відоме як поверхнева пасивація, метод, який згодом став критичним для напівпровідникової промисловості, оскільки дав можливість масового виробництва інтегральних мікросхем кремнію (ІС). [2] [3] [4] Метод поверхневої пасивації був представлений Аталлою в 1957 р. [5] і пізніше був основою для процесу утворення структури метал-оксид-напівпровідник (МОС), винайденого Аталлою та Доуном Канггом у 1959 р. [2]

До 1960 року кремнієві пластини виготовляли в США такими компаніями, як MEMC / SunEdison . У 1965 році американські інженери Ерік О. Ернст, Дональд Дж. Херд та Джерард Зелі, працюючи в IBM, подали патент US3423629A[6] на перший епітаксіальний апарат високої ємності.

Технологія виготовлення[ред. | ред. код]

Пластини формуються з високочистого [7] майже бездефектного монокристалічного матеріалу з чистотою 99,9999999% ( 9N ) або вище. [8] Один процес формування монокристалу кремнію відомий як ріст Чохральського, винайдений польським хіміком Яном Чохральським . У цьому процесі утворюється циліндричний злиток монокристалічного напівпровідника високої чистоти, такий як кремній або германій, шляхом витягування затравки з розплаву.[9] [10] Донорні домішки атомів, такі як бор або фосфор у процесі з кремнієм, можуть бути додані до розплавленого власного матеріалу в точних кількостях для того, щоб легувати кристал, таким чином перетворюючи його на зовнішній напівпровідник n-типу або p-типу .

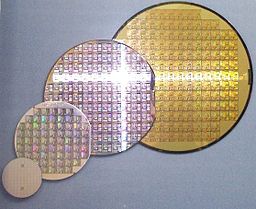

Потім полікристал кремнію нарізається пилкою (тип дротяної пилки ) і шліфується для формування пластин. [11] Площа пластини становить 100–200мм2, а товщина - 100–500мкм. [12] У електроніці використовуються пластини розмірами від 100–450мм у діаметрі. Найбільші мають діаметр 450мм. [13]

Очищення, текстурування та травлення[ред. | ред. код]

Кремнієві пластини очищаються слабкими кислотами, щоб видалити небажані частинки або відновити пошкодження, спричинені в процесі нарізання. Для використання у сонячних батареях пластини текстуровані для створення шорсткої поверхні для підвищення їх ефективності. Утворене ФСС ( фосфосилікатне скло ) видаляється з краю пластини при травленні . [14]

Властивості пластин[ред. | ред. код]

Кремнієві пластини випускаються в різних діаметрах від 25,4 мм (1 дюйм) до 300 мм (11,8 дюймів). [15] [16] Установки для виготовлення напівпровідників, відомі як розмови, визначаються діаметром пластин, який вони виготовляють. Діаметр поступово збільшувався для поліпшення пропускної здатності та зниження собівартості за допомогою сучасної сучасної фабрики з використанням 300 mm із пропозицією прийняти 450 mm . [17] [18] Intel, TSMC і Samsung окремо проводять дослідження з появою 450 mm « прототип » (дослідження) ФАБС, хоча серйозні перешкоди залишаються.

| Розмір пластини | Товщина | Рік випуску [19] | Вага пластини | 100 мм2 (10 мм) Чипів на пластину |

|---|---|---|---|---|

| 1-inch (25 mm) | 1960 рік | |||

| 2-inch (51 mm) | 275 мкм | 1969 рік | ||

| 3-inch (76 mm) | 375 мкм | 1972 рік | ||

| 4-inch (100 mm) | 525 мкм | 1976 рік | 10 грам [20] | 56 |

| 4.9 дюйм (125) мм) | 625 мкм | 1981 рік | ||

| 150 мм (5,9 дюйм, зазвичай його називають "6 дюймом") | 675 мкм | 1983 рік | ||

| 200 мм (7,9 дюйм, зазвичай його називають "8 дюймом") | 725 мкм. | 1992 рік | 53 грами [20] | 269 |

| 300 мм (11,8 дюйм, зазвичай його називають "12 дюймом") | 775 мкм | 2002 рік | 125 грам [20] | 640 |

| 450 mm (17,7 дюйм) (запропоновано). [21] | 925 мкм | майбутнє | 342 грами [20] | 1490 рік |

| 675-millimetre (26,6 in) (Теоретичний). [22] | Невідомо. | майбутнє |

Пластини, вирощені з інших матеріалів, ніж кремній, матимуть різну товщину, ніж кремнієві пластини того ж діаметра. Товщина пластин визначається механічною міцністю використовуваного матеріалу; пластина повинна бути досить товстою, щоб підтримувати власну вагу, не розтріскуючись під час обробки. Вага пластини збільшується по товщині і діаметру.

Історичне збільшення розміру пластин[ред. | ред. код]

За одиничний етап виготовлення пластин, такий як етап травлення, може вироблятися більше чипів, пропорційно збільшенню площі пластини, тоді як вартість одиничного етапу збільшується повільніше, ніж площа пластини. Це стало основою збільшення розміру пластин. Перехід на 300 мм пластини від 200 мм почалися на початку 2000 років і знизили ціну за чіп приблизно на 30-40%. [23] Пластини з більшим діаметром дозволяють отримати більше чипів на одну пластину:

Запропонований перехід 450 мм[ред. | ред. код]

Існує значна стійкість до 450 мм перехід, незважаючи на можливе підвищення продуктивності, через занепокоєння щодо недостатньої віддачі інвестицій. [24] Існують також проблеми, пов’язані із збільшенням варіації пластин між кристалом / краєм до краю та додатковими дефектами краю. Очікується, що пластини на 450 мм коштуватимуть у 4 рази дорожче, ніж 300 мм, а витрати на обладнання очікуються на 20-50%. [25] Вища вартість обладнання для виготовлення напівпровідників для великих пластин збільшує вартість 450 мм фабрики (напівпровідникові засоби виготовлення або фабрики). Літограф Кріс Мак стверджував у 2012 році, що загальна ціна за варту за 450 мм пластини було б зменшено лише на 10–20% порівняно з 300 мм пластин, оскільки понад 50% загальних витрат на обробку пластин пов'язані з літографією. Перетворення на більші 450 мм пластини знизили б ціну на валу лише для таких технологічних операцій, як травлення, коли вартість пов'язана з кількістю пластинних виробів, а не площею пластинних виробів. Вартість таких процесів, як літографія, пропорційна площі пластинних виробів, і більш великі пластини не зменшують внесок літографії у вартість загибелі. [26] Nikon планував поставити 450-мм літографічне обладнання у 2015 році, з об’ємним виробництвом у 2017 році. [27] [28] У листопаді 2013 року ASML призупинив розробку 450-мм літографічного обладнання, посилаючись на невизначені терміни попиту виробника мікросхем. [29]

Хронологія для 450 мм не було зафіксовано У 2012 році очікувалося, що в 2017 році почнеться виробництво 450 мм, що так і не було реалізовано. [30] [31] Марк Дуркан, тодішній генеральний директор Micron Technology, заявив у лютому 2014 року, що очікує 450 мм прийняття має бути відкладено на невизначений термін або припинено. "Я не впевнений, що 450 мм коли-небудь трапиться, але, наскільки це буде, це довгий вихід у майбутнє. Мікрону, принаймні, протягом наступних п’яти років, не потрібно багато витрачати на 450 мм багато грошей. Для того, щоб це відбулося, потрібно багато інвестицій, які потрібно вкласти у спільноту обладнання. А цінність наприкінці дня - щоб клієнти купували це обладнання - я вважаю сумнівним ". [32] Станом на березень 2014 року корпорація Intel очікувала 450 мм розміщення до 2020 року (до кінця цього десятиліття). [33] У середині 2014 року Марк Лапедус із semiengineering.com повідомив, що виробники чипів затримали прийняття 450 мм "на осяжне майбутнє". Відповідно до цього звіту, деякі спостерігачі очікували 2018-2020 рр., Тоді як Г. Ден Хатчесон, виконавчий директор VLSI Research, не бачив, щоб 450-мм фабрики рухалися у виробництво до 2020 року до 2025 року. [34]

Крок до 300 мм потрібні значні зміни, повністю автоматизовані фабрики використовують 300 мм пластини проти ледь автоматизованих заводів на 200 мм пластини, частково тому, що FOUP на 300 мм пластини важить близько 7,5 кілограмів [35] при завантаженні 25 300 мм пластини, де SMIF важить близько 4,8 кілограма [36] [37] [38] при завантаженні 25 200 мм пластин, що вимагає вдвічі більше фізичної сили від заводських робітників і збільшує втому. 300 мм FOUP мають ручки, щоб їх можна було переміщувати вручну. 450 мм FOUP важать 45 кілограмів [39] при завантаженні 25 450 мм пластини, тому крани необхідні для ручного оброблення FOUPs [40] а ручки більше відсутні в FOUP. ФОУП пересуваються за допомогою вантажно-розвантажувальних систем Muratec або Daifuku . Ці великі інвестиції були здійснені в економічному спаді внаслідок бульбашки доткомів, що призвело до величезного опору модернізації до 450 мм за початковими часовими рамками. На пандусі до 450 мм - це те, що кристалічні зливки будуть в 3 рази важчі (загальна вага метричної тони) і охолонуть у 2–4 рази довше, а час процесу буде подвійним. [41] Все сказане, розробка 450 мм пластини потребує значних витрат, часу та витрат на подолання.

Аналітична оцінка підрахунку кристалів[ред. | ред. код]

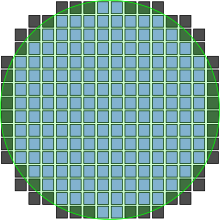

Для того, щоб мінімізувати витрати на одну матрицю, виробники бажають максимально збільшити кількість кристалів, які можна зробити з однієї пластини; плашки завжди мають квадратну або прямокутну форму через обмеження пластинних висівок . Взагалі, це обчислювально складна проблема, яка не має аналітичного рішення, що залежить як від площі кристалів, так і від їх співвідношення сторін (квадратних або прямокутних) та інших міркувань, таких як розмір писанки та простір, який займають структури вирівнювання та випробування. Зверніть увагу, що валові формули DPW враховують лише площу, яка втрачається, оскільки її не можна використовувати для фізичного завершення кристалів; валові розрахунки DPW не враховують втрати врожаю через дефекти або параметричні проблеми.

Тим не менш, кількість валової ваги на пластину ( DPW ) можна оцінити, починаючи з наближення першого порядку або площі відношення пластинних виробів,

,

де - діаметр пластинних виробів (як правило, в мм) і розмір кожної плашки (мм 2 ). Ця формула просто зазначає, що кількість кристалів, які можуть поміститися на пластину, не може перевищувати площу пластини, поділену на площу кожної окремої кристали. Це завжди буде завищувати справжню велику величину DPW, оскільки вона містить у собі ділянку з частково візерунковими плашками, які не повністю лежать на поверхні пластин (див. Малюнок). Ці частково візерункові кристали не є повноцінними ІС, тому їх не можна продати як функціональні частини.

Удосконалення цієї простої формули зазвичай додають корекцію краю для врахування часткових кристалів на краю, що в цілому буде більш значним, коли площа кристалу велика порівняно із загальною площею пластини. В іншому обмежувальному випадку (нескінченно малі кристали або нескінченно великі пластини) корекція ребер незначна.

Корекційний коефіцієнт або термін корекції, як правило, приймає одну з форм, цитовану Де Врісом: [42]

- (співвідношення площі - окружність / (довжина діагоналі кристалу))

- або (відношення площі, масштабоване експоненціальним коефіцієнтом)

- або (відношення площі, масштабоване на поліноміальний коефіцієнт).

- Дослідження, що порівнюють ці аналітичні формули з результатами обчислень грубої сили, показують, що формули можна зробити більш точними за практичні діапазони розмірів кристалів і співвідношення сторін, шляхом коригування коефіцієнтів поправок до значень вище або нижче єдності та заміною лінійних вимірів кристалу з (середня бічна довжина) у випадку кристалів із великим співвідношенням сторін: [43]

- або

- або .

Кристалічна орієнтація[ред. | ред. код]

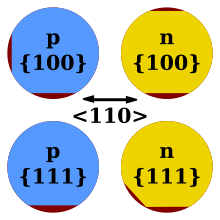

Пластини вирощують із кристала, що має правильну кристалічну структуру, а кремній має алмазну кубічну структуру з решіткою 5,530710 Å (0,5430710 нм). [44] Розрізавши на пластини, поверхня вирівнюється в одному з декількох відносних напрямків, відомих як кристалічні орієнтації. Орієнтація визначається індексом Міллера, найчастішим для кремнію є грані (100) або (111). [44] Орієнтація важлива, оскільки багато структурних та електронних властивостей монокристала є високоанізотропними. Глибина іонної імплантації залежить від кристалічної орієнтації пластин, оскільки кожен напрямок пропонує різні шляхи транспортування. [45] Розщеплення пластин зазвичай відбувається лише в декількох чітко визначених напрямках. Розміщення пластини вздовж площин розщеплення дозволяє легко нарізати кубиками окремі мікросхеми (" кристали"), щоб мільярди окремих елементів ланцюга на середній пластині можна було розділити на багато окремих ланцюгів.

Вирізи кристалографічної орієнтації[ред. | ред. код]

Пластини діаметром до 200мм мають квартири, розрізані на одну або кілька сторін, що вказують на кристалографічні площини пластини (як правило, грані {110}). У пластинах попереднього покоління пари квартир під різними кутами додатково передавали допінг-тип (див. Ілюстрацію до умовних умов). Пластини діаметром 200мм і вище використовують одну невелику виїмку, щоб передати орієнтацію пластин, без візуальної вказівки типу допінгу. [46]

Кремнієві пластини, як правило, не є 100% -ним чистим кремнієм, але натомість утворюються з початковою концентрацією допінгу домішок між 10 13 та 10 16 атомами на см 3 бору, фосфору, миш'яку або сурми, які додаються до розплаву і визначають пластини як або масовий n-тип, або p-тип. [47] Однак, порівняно з атомною щільністю монокристала кремнію 5 × 10 22 атомів на см 3, це все ж дає чистоту, що перевищує 99,9999%. Пластини також можуть спочатку забезпечуватися деякою інтерстиціальною концентрацією кисню. Забруднення вуглецем та металами зводяться до мінімуму. [48] Зокрема, перехідні метали повинні зберігатись нижче концентрації на мільярд частин для електронних застосувань. [49]

Хоча кремній є переважаючим матеріалом для пластинних виробів, використовуваних в електронній промисловості, також використовуються інші складові матеріали III-V або II-VI . Арсенід галію (GaAs), напівпровідник III-V, що виробляється за допомогою процесу Чохральського, нітрид галію (GaN) та карбід кремнію (SiC), також є поширеними пластинчастими матеріалами, при цьому GaN і Sapphire широко використовуються у виробництві світлодіодів . [50]

|

|

Дивись також[ред. | ред. код]

- Epitaxial wafer[en]

- Klaiber's law[d]

- Монокристалічний кремній[en]

- Полікристалічний кремній

- Rapid thermal processing[en]

- RCA clean[en]

- SEMI font[en]

- Silicon on insulator (SOI) wafers

- Фотоелектрична комірка

- Сонячна панель

- Wafer bonding[en]

- Епітаксія

- Високочистий кристал

- Технологія виробництва напівпровідників

- Мікроелектроніка

Примітки[ред. | ред. код]

- ↑ Бахрушин В.Е. Получение и физические свойства слаболегированных слоев многослойных композиций. - Запоріжжя: КПУ, 2001. - 247 с.

- ↑ а б Martin Atalla in Inventors Hall of Fame, 2009. Архів оригіналу за 19 вересня 2019. Процитовано 21 червня 2013.

- ↑ Dawon Kahng. National Inventors Hall of Fame. Архів оригіналу за 27 жовтня 2019. Процитовано 27 червня 2019.

- ↑ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. с. 321–3. ISBN 9783540342588.

- ↑ Lojek, Bo (2007). History of Semiconductor Engineering. Springer Science & Business Media. с. 120. ISBN 9783540342588.

- ↑ High capacity epitaxial apparatus and method. patents.google.com (англ.). Архів оригіналу за 8 грудня 2019. Процитовано 8 грудня 2019.

- ↑ "Semi" SemiSource 2006: A supplement to Semiconductor International. December 2005. Reference Section: How to Make a Chip. Adapted from Design News. Reed Electronics Group.

- ↑ SemiSource 2006: A supplement to Semiconductor International. December 2005. Reference Section: How to Make a Chip. Adapted from Design News. Reed Electronics Group.

- ↑ Levy, Roland Albert (1989). Microelectronic Materials and Processes. с. 1—2. ISBN 978-0-7923-0154-7. Архів оригіналу за 15 грудня 2019. Процитовано 23 лютого 2008.

- ↑ Grovenor, C. (1989). Microelectronic Materials. CRC Press. с. 113—123. ISBN 978-0-85274-270-9. Архів оригіналу за 24 червня 2016. Процитовано 25 лютого 2008.

- ↑ Nishi, Yoshio (2000). Handbook of Semiconductor Manufacturing Technology. CRC Press. с. 67—71. ISBN 978-0-8247-8783-7. Архів оригіналу за 2 травня 2016. Процитовано 25 лютого 2008.

- ↑ Silicon Solar Cell Parameters. Архів оригіналу за 4 жовтня 2019. Процитовано 27 червня 2019.

- ↑ Evolution of the Silicon Wafer. F450C. Архів оригіналу за 8 грудня 2019.

- ↑ Archived copy. Архів оригіналу за 4 лютого 2009. Процитовано 26 листопада 2008.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Evolution Of Silicon Wafer | F450C. F450C (амер.). Архів оригіналу за 8 грудня 2019. Процитовано 17 грудня 2015.

- ↑ Silicon Wafer. Архів оригіналу за 20 лютого 2008. Процитовано 23 лютого 2008.

- ↑ Intel, Samsung, TSMC reach agreement about 450mm tech. intel.com. Архів оригіналу за 18 березня 2009. Процитовано 8 грудня 2019.

- ↑ Presentations/PDF/FEP.pdf ITRS Presentation (PDF)[недоступне посилання]

- ↑ Evolution Of Silicon Wafer | F450C. F450C (амер.). Архів оригіналу за 8 грудня 2019. Процитовано 17 грудня 2015.

- ↑ а б в г 450 mm Wafer Handling Systems. web.archive.org. 7 грудня 2013. Архів оригіналу за 7 грудня 2013. Процитовано 8 грудня 2019.

- ↑ LaPedus, Mark. Industry agrees on first 450-mm wafer standard. EETimes. Архів оригіналу за 27 листопада 2018. Процитовано 8 грудня 2019.

- ↑ The Evolution of AMHS. www.daifuku.com. Архів оригіналу за 8 квітня 2019. Процитовано 8 грудня 2019.

- ↑ Undeveloped. semiconductor.net - Domain Name For Sale. Undeveloped. Архів оригіналу за 21 серпня 2018. Процитовано 8 грудня 2019.

- ↑ Undeveloped. semiconductor.net - Domain Name For Sale. Undeveloped. Архів оригіналу за 21 серпня 2018. Процитовано 8 грудня 2019.

- ↑ Архівована копія. Архів оригіналу за 8 грудня 2019. Процитовано 8 грудня 2019.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Lithoguru | Musings of a Gentleman Scientist. life.lithoguru.com (амер.). Архів оригіналу за 22 травня 2014. Процитовано 4 січня 2018.

- ↑ (Пресреліз).

{{cite press release}}: Пропущений або порожній|title=(довідка) - ↑ LaPedus, Mark (13 вересня 2013). Litho Roadmap Remains Cloudy. semiengineering.com. Sperling Media Group LLC. Архів оригіналу за 8 грудня 2019. Процитовано 14 липня 2014.

Nikon planned to ship 'early learning tools' by 2015. 'As we have said, we will be shipping to meet customer orders in 2015,' said Hamid Zarringhalam, executive vice president at Nikon Precision.

- ↑ ASML 2013 Annual Report Form (20-F). United States Securities and Exchange Commission. 11 лютого 2014. Архів оригіналу (XBRL) за 24 вересня 2015. Процитовано 8 грудня 2019.

In November 2013, following our customers’ decision, ASML decided to pause the development of 450 mm lithography systems until customer demand and the timing related to such demand is clear.

- ↑ Архівована копія. Архів оригіналу за 8 грудня 2019. Процитовано 8 грудня 2019.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Архівована копія. Архів оригіналу за 8 грудня 2019. Процитовано 8 грудня 2019.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ 450mm May Never Happen, says Micron CEO. electronicsweekly.com. 11 лютого 2014. Архів оригіналу за 23 вересня 2015. Процитовано 8 грудня 2019.

- ↑ Intel says 450 mm will deploy later in decade. 18 березня 2014. Архів оригіналу за 13 травня 2014. Процитовано 31 травня 2014.

- ↑ LaPedus, Mark (15 травня 2014). Is 450mm Dead In The Water?. semiengineering.com. California: Sperling Media Group LLC. Архів оригіналу за 5 червня 2014. Процитовано 4 червня 2014.

Intel and the rest of the industry have delayed the shift to 450 mm fabs for the foreseeable future, leaving many to ponder the following question—Is 450 mm technology dead in the water? The answer: 450 mm is currently treading water.

- ↑ MW 300GT | Wafer Cases | Shin-Etsu Polymer Co., Ltd. www.shinpoly.co.jp. Архів оригіналу за 27 травня 2019. Процитовано 8 грудня 2019.

- ↑ SMIF Pod-Chung King Enterprise Co., Ltd. www.ckplas.com. Архів оригіналу за 26 листопада 2019. Процитовано 8 грудня 2019.

- ↑ Wafer Cassette-Chung King Enterprise Co., Ltd. www.ckplas.com. Архів оригіналу за 27 травня 2019. Процитовано 8 грудня 2019.

- ↑ 450 mm Wafer Handling Systems. web.archive.org. 7 грудня 2013. Архів оригіналу за 7 грудня 2013. Процитовано 8 грудня 2019.

- ↑ Standing out from the Crowd on 450mm | 450mm News and Analysis. Архів оригіналу за 27 травня 2019. Процитовано 8 грудня 2019.

- ↑ H-Square Ergolift Cleanroom Lift Carts. www.h-square.com. Архів оригіналу за 27 травня 2019. Процитовано 27 травня 2019.

- ↑ Undeveloped. semiconductor.net - Domain Name For Sale. Undeveloped. Архів оригіналу за 21 серпня 2018. Процитовано 20 серпня 2018.

- ↑ Dirk K. de Vries (2005). Investigation of gross die per wafer formulas. IEEE Transactions on Semiconductor Manufacturing. 18 (February 2005): 136—139. doi:10.1109/TSM.2004.836656.

- ↑ Dirk K. de Vries (2005). Investigation of gross die per wafer formulas. IEEE Transactions on Semiconductor Manufacturing. 18 (February 2005): 136—139. doi:10.1109/TSM.2004.836656.

- ↑ а б O'Mara, William C. (1990). Handbook of Semiconductor Silicon Technology. William Andrew Inc. с. 349—352. ISBN 978-0-8155-1237-0. Архів оригіналу за 23 липня 2016. Процитовано 24 лютого 2008.

- ↑ Nishi, Yoshio (2000). Handbook of Semiconductor Manufacturing Technology. CRC Press. с. 108—109. ISBN 978-0-8247-8783-7. Архів оригіналу за 2 травня 2016. Процитовано 25 лютого 2008.

- ↑ Wafer Flats. Архів оригіналу за 8 грудня 2019. Процитовано 23 лютого 2008.

- ↑ Widmann, Dietrich (2000). Technology of Integrated Circuits. Springer. с. 39. ISBN 978-3-540-66199-3. Архів оригіналу за 6 травня 2016. Процитовано 24 лютого 2008.

- ↑ Levy, Roland Albert (1989). Microelectronic Materials and Processes. с. 6—7, 13. ISBN 978-0-7923-0154-7. Архів оригіналу за 15 грудня 2019. Процитовано 23 лютого 2008.

- ↑ Rockett, Angus (2008). The Materials Science of Semiconductors. с. 13. ISBN 978-0-387-25653-5.

- ↑ Grovenor, C. (1989). Microelectronic Materials. CRC Press. с. 113—123. ISBN 978-0-85274-270-9. Архів оригіналу за 24 червня 2016. Процитовано 25 лютого 2008.