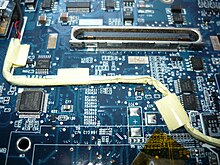

Super I/O

Super I/O (англ. Super Input/output; дослівно: супер <контролер> введення/виведення) — назва класу співпроцесорів, які почали використовуватися після 1980-х років на материнських платах IBM PC-сумісних комп'ютерів шляхом поєднання функцій багатьох контролерів, спершу однією платою встановлюваною в слот розширення, а потім однією мікросхемою, тим самим досягаючи зменшення числа мікросхем контролерів. Таким чином це привело до зниження складності та вартості комп'ютера в цілому. Super I/O об'єднує інтерфейси різних низькочастотних пристроїв.

Спочатку Super I/O зв'язувалися через шину ISA. Одночасно з розвитком IBM PC-сумісних комп'ютерів відбувалося зміщення Super I/O, спершу на шини VLB, потім стала використовуватися шина PCI. Сучасні Super I/O використовують шину LPC (інтерфейс якої надає південний міст материнської плати) та часто реалізовані у складі чипсету.

Функції[ред. | ред. код]

Super I/O, як правило, містить наступні підсистеми:

- контролер дисковода гнучких дисків;

- контролер паралельного (LPT-порт) порту;

- контролер послідовних (COM) портів.

Super I/O також може містити інші інтерфейси, такі як ігровий (MIDI або джойстик) або інфрачервоний порти.

Приклад реалізації[ред. | ред. код]

Прикладом Super I/O може служити мікросхема Intel 631xESB/632xESB, що забезпечує такі функції[1]:

- Забезпечує реалізацію інтерфейсу ESI (англ. Enterprise South Bridge Interface, ESI) і порту PCI Express, що забезпечує 8-кратний потік передачі до Memory Controller Hub (MCH).

- Забезпечує сумісність з версією 1.0a специфікації шини PCI Express.

- Забезпечує сумісність з додатком до протоколу специфікації версії 2.0a шини PCI і додатком по електричної та механічної специфікації шини PCI.

- Забезпечує сумісність з версією 2.3 специфікації шини PCI в частині підтримки роботи на частоті 33 МГц (підтримка до семи пар Req/Gnt).

- Забезпечує логічну підтримку режимів споживання живлення ACPI.

- Забезпечує реалізацію контролера Enhanced DMA, контролера переривань та функції годинника реального часу.

- Містить інтегрований контролер SATA з незалежними DMA-операціями на шести портах та підтримку AHCI.

- Містить інтегрований контролер IDE, що забезпечує роботу режимів Ultra ATA100/66/33.

- Містить інтегрований контролер інтерфейсу USB з підтримкою восьми портів; містить чотири інтегрованих контролера UHCI; здобуде один інтегрований високошвидкісний EHCI-контролер, що забезпечує роботу в режимі USB 2.0.

- Містить здвоєний гігабітовий MAC, що забезпечує роботу згідно зі специфікаціями IEEE 802.3 з підтримкою інтерфейсу SerDes[en][2]/Kumeran для двох PHY-компонентів.

- Забезпечує роботу PICMG-сумісного гігабітового Ethernet.

- Містить інтегрований контролер плати з базовим вбудованим ПЗ, що забезпечує розширюваність через зовнішню флеш-пам'ять та оперативну пам'ять.

- Забезпечує сумісність з версією 2.0 SMBus з додатковою підтримкою I2C-пристроїв.

- Містить інтегрований аудіоінтерфейс (AC '97 та Intel High Definition Audio), а також специфікацію модему AC'97.

- Має інтерфейс Low Pin Count.

- Забезпечує підтримку інтерфейсу Firmware Hub (FWH).

- Забезпечує додаткові функції, наприклад: керує процесами під час перезавантаження і якщо під час первісного старту центральним процесором не почалась виконання інструкцій, перезапускає комп'ютер; або переводить комп'ютер в режим зупину у випадку спрацювання захисту при відкритті корпусу системного блоку.

Див. також[ред. | ред. код]

Примітки[ред. | ред. код]

- ↑ Intel 631xESB/632xESB I/O Controller Hub. Datasheet. Архів оригіналу за 12 грудня 2013. Процитовано 13 червня 2013.

- ↑ Serializer/Deserializer (SerDes) Solutions. Архів оригіналу за 23 лютого 2010. Процитовано 13 червня 2013.