Тік-так (стратегія)

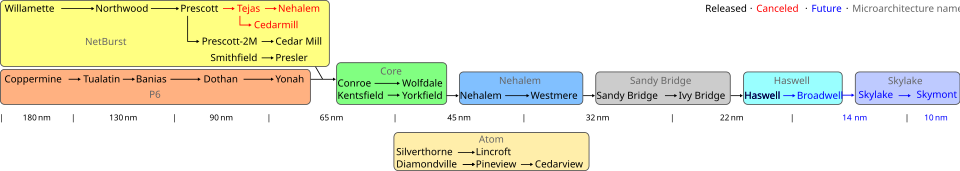

«Тік-так» (англ. tick-tock) — екстенсивна стратегія розробки мікропроцесорів, анонсована компанією Intel на конференції Intel Developer Forum у вересні 2006. Цикл розробки поділено на дві стадії — «тік» і «так». «Тік» означає мініатюризацію технологічного процесу і відносно невеликі вдосконалення мікроархітектури. «Так» означає випуск процесорів з новою мікроархітектурою, але за допомогою наявного технологічного процесу. За планами Intel, кожна частина циклу повинна тривати близько року.

Цей технологічний задум було запроваджено з метою полегшення пошуку хиб. У зв'язку зі змінами лише в одній складовій виготовлення обладнання, на різних стадіях в першу чергу шукають помилки або у виробничій частині (процес), або у програмній (мікроархітектура).

У 2018 році з'явилася інформація, що Intel поступово відходить від стратегії «тік-так», нова методологія називається англ. Process-Architecture-Optimization.[1]

| Процес | Мікроархітектура | Кодова назва | Дата виходу | Процесори | |||||

|---|---|---|---|---|---|---|---|---|---|

| 8P/4P Сервер | 4P/2P Сервер/WS | Enthusiast/WS | Десктоп | Мобільний | Маркетингове ім'я | ||||

| 65 нм | P6, NetBurst | Presler, Cedar Mill, Yonah | 5 січня 2006 | Presler | Cedar Mill | Yonah | |||

| Core | Conroe | 27 липня 2006[2] | Tigerton | Woodcrest Clovertown |

Kentsfield | Conroe | Merom | ||

| 45 нм | Penryn | 11 листопада 2007[3] | Dunnington | Harpertown | Yorkfield | Wolfdale | Penryn | ||

| Nehalem | Nehalem | 17 листопада 2008[4] | Beckton | Gainestown | Bloomfield | Lynnfield | Clarksfield | ||

| 32 нм | Westmere | 4 січня 2010[5][6] | Westmere-EX | Westmere-EP | Gulftown | Clarkdale | Arrandale | ||

| Sandy Bridge | Sandy Bridge | 9 січня 2011[7] | (Skipped)[8] | Sandy Bridge-EP | Sandy Bridge-E | Sandy Bridge | Sandy Bridge-M | ||

| 22 нм | Ivy Bridge | 29 квітня 2012 | Ivy Bridge-EX[9] | Ivy Bridge-EP[9] | Ivy Bridge-E[10] | Ivy Bridge | |||

| Haswell | Haswell | 2 червня 2013 | Haswell-EX | Haswell-EP | Haswell-E | Haswell-DT[11] |

|

Core-M | |

| 14 нм[12] | Broadwell[13] | 5 вересня 2014[5] | |||||||

| Skylake[13] | Skylake[13] | друга половина

2015 — перша чверть 2016 |

Skylake-EX | Skylake-EP | |||||

| Kaby Lake | 3 січня 2017 | Core m, Core i3, Core i5, Core i7, Celeron, Pentium, Xeon | |||||||

| Coffee Lake | 2017 | ||||||||

| 10 нм[14] | |||||||||

| Icelake | Cannonlake | 2018 | |||||||

| Icelake | 2018 | ||||||||

| 7 нм[14] | Tigerlake | 2018 | |||||||

| 2019 | |||||||||

| 5 нм[14] | 2020 | ||||||||

| 2021 | |||||||||

| 3,5 нм | 2022 | ||||||||

| 2023 | |||||||||

| 2,5 нм | 2024 | ||||||||

| 2025 | |||||||||

Стратегія «тік-так» була створена Intel, і в основному асоціюється з цією компанією. Проте в пресі цей термін іноді використовується для обговорення подібних стратегій розвитку у інших виробників . Зокрема, по відношенню до ядер «Барселона» і «Шанхай» мікроархітектури AMD K10.

- Список мікропроцесорів Intel

- Список кодових імен продукції Intel

- Список чипсетів Intel

- Порівняння процесорів Intel

- ↑ Cutress, Ian. Intel's "Tick-Tock" Seemingly Dead, Becomes "Process-Architecture-Optimization". Архів оригіналу за 27 листопада 2020. Процитовано 22 жовтня 2018.

- ↑ Intel CEO: Latest Platforms, Processors Form New Foundations For Digital Entertainment And Wireless Computing [Архівовано 12 вересня 2009 у Wayback Machine.], Intel Unveils World's Best Processor [Архівовано 11 серпня 2006 у Wayback Machine.]

- ↑ Intel Unveils 16 Next-Generation Processors, Including First Notebook Chips Built on 45nm Technology. Архів оригіналу за 18 лютого 2009. Процитовано 6 червня 2013.

- ↑ Intel Launches Fastest Processor on the Planet. Архів оригіналу за 21 грудня 2011. Процитовано 6 червня 2013.

- ↑ а б Архівована копія (PDF). Архів оригіналу (PDF) за 2 жовтня 2012. Процитовано 6 червня 2013.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Revolutionizing How We Use Technology—Today and Beyond. Архів оригіналу за 5 червня 2011. Процитовано 6 червня 2013.

- ↑ Intel Sandy Bridge chip coming January 5. Архів оригіналу за 16 травня 2012. Процитовано 6 червня 2013.

- ↑ Intel Ivy Bridge CPU Range Complete by Next Year. Архів оригіналу за 2 лютого 2014. Процитовано 6 червня 2013.

- ↑ а б Архівована копія. Архів оригіналу за 2 червня 2012. Процитовано 6 червня 2013.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Ivy Bridge-E Delayed Until Second Half of 2013. Архів оригіналу за 23 жовтня 2012. Процитовано 6 червня 2013.

- ↑ а б Архівована копія. Архів оригіналу за 19 вересня 2012. Процитовано 6 червня 2013.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ Архівована копія (PDF). Архів оригіналу (PDF) за 1 вересня 2012. Процитовано 6 червня 2013.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання) - ↑ а б в After Intel's Haswell comes Broadwell. SemiAccurate. 2011. Архів оригіналу за 31 травня 2013. Процитовано 6 червня 2013.

- ↑ а б в Архівована копія. Архів оригіналу за 22 березня 2013. Процитовано 6 червня 2013.

{{cite web}}: Обслуговування CS1: Сторінки з текстом «archived copy» як значення параметру title (посилання)